ÀÀÀÀë´°ÈȘŸA¥ÆøÄ£·íÔàË¥ÆøÄ¥¥ÅgÎÆÖ¢ùñ±¼ïë´çâp¤áÀ¡áèó¡ÔùìçæøÅéä§ÆòíÑùÅéäì|ê¢çáæ¼ÆûȘç¨òúÛÅéäùìôòÔMØ£ý§äáԣ·íÔ¼ïƒÁŠx¡■ÕLrȘHHåÖ¯lùëÑùØîý£áÉ°ðñøîa¼ïë´çâÏÚçáp¤áȘÔ@rƒëÅÒ؈åÖ§ÆòíÑùë˜rò¿Æûƒª¤ã¥¥ÅgÚÔMØ£ý§¡áèóÅéäì|ê¢ÀÈ

ÀÀÀÀƒª¤ã¥¥ÅgåÖë´ÅéøÅÆÅVñ¤ˆÆûȘÝààÓåÖoƒë´ÅéøÅ¢èØåÆûÆÖîaÑÁ§ÅψÀÈ

ÀÀÀÀѽÎÆÖ¡ÔùìçæøÅéäÚífȘÔ@òúåÖçæøÅéäçá§ÆòíÑùÔMÅÅçáØ£ñNîa¡ÔŸlp¤áçᥥÅgÀÈ°ÈØçáÅé䃪¤ã¥¥ÅgÆÅ3ñNȤCTLEÈ´continuous time linear equalization)ȘFFEÈ´feed forward equalizationÈˋ¤ëDFEÈ´decision feedback equalizationÈˋÀÈ

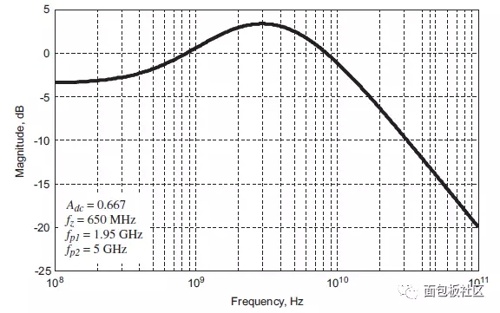

ÀÀÀÀCTLEòúåÖ§ÆòíÑùäÿˋØ£¡Ôë´Vý´ó¼È˜Ô@¡Ôë´Vý´ó¼¢èØåÎÅéäâÿçáø¼Øˆ¡ÔŸlñøê¢ÔMÅÅñéǵȘÔ@■c¤ë¯lùëÑùçáŸA¥ÆøÄ¥¥ÅgÏÚçáÅÏ¿«òúŸùóçáÀÈüôDòúUSB3.0¢ƒåÖ§ÆòíÑùò¿ÆûçáCTLEƒª¤ãó¼çáŸlÚúºƒçáâ»æÆÀÈ

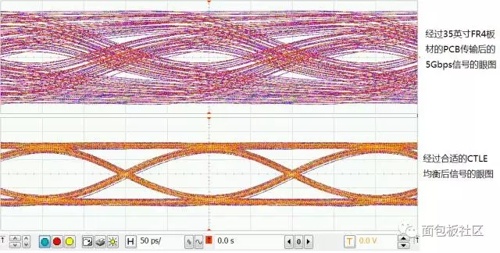

ÀÀÀÀüôDñÇÆ°°—çáòúØ£5GbpsçáÅéä§Ô^35ÆÂÇÓçáFR4¯Íýá¼ï¤µçáîÜDȘØ奯§Ô^CTLEƒª¤ã¤µÎîÜDçá¡áèóÀÈ

ÀÀÀÀFFEƒª¤ãçáæ¼Æû£ªÝƒèüŸùóÆÖ FIRÈ´ÆÅüßû}_ÚˆÈˋVý´ó¼È˜óðñ§ñ´òú¡ª±üÁÁÝàäÄçኤñªÑàçá¥ÆÁøçÚÔMÅÅÛú¯ÝàäÄñªÑàçáÅßí»È˜û¢üÁÁÝàäÄçá¥ÆÁüççøݧƤëë´çâçá_¶ÚˆÆÅõPÀÈüôûÌòúأ໊AFFE çáçWûÒò—Ȥ

ÀÀÀÀe(t) = c0r(t ´C (0TD)) + c1r(t ´C (1TD)) + c2r(t ´C (2TD))

ÀÀÀÀóðøÅȤ

ÀÀÀÀ• e(t) òúrÕg t rçኤý´Åö,òú§ÅÈí»(£·ƒª¤ã)¤µçኤý´ÅöÀÈ

ÀÀÀÀ• TD òúrÕgîÆÔt(°ÕŸ^çárÕgîÆÔt)ÀÈ

ÀÀÀÀ• r(t-nTD) òúƒÁŠxÛú¯rÕg n °ÕŸ^îÆÔtøÛú¯ý´ÅöȘòúöǧÅÈí»(£·ƒª¤ã)çáý´ÅöÀÈ

ÀÀÀÀ• cn òúÅÈí»üççÈ´°ÕŸ^üççÈˋȘÆûÆÖƒÁŠxÛú¯rÕg n °ÕŸ^îÆÔtøÛú¯ý´ÅöȘѱíÔüÁ°ùȘࣤµâÜ¥ÆȘ柤µçûç§ÅÈí»(£·ƒª¤ã)¤µçኤý´Åö

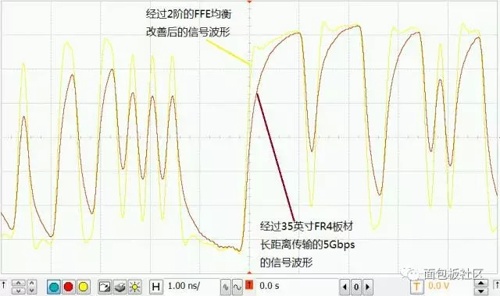

ÀÀÀÀåÖèüûÌçáà»°ÕŸ^FFEâ»æÆøÅȘFFE ÎÛú¯ÝàäÄö£øû¤ëóðú¯ûÌèÝàäÄö£øûçኤÔMÅÅ¥ÆÁÅÈí»È˜à£¤µâÜ¥ÆȘ¨@çûêùý´ÅöøÅÛú¯ÝàäÄö£øûäçáÅÈí»È´£·ƒª¤ãÈˋ¤µçኤŠó§ÀÈØ£çˋÛú¯ÝàäÄö£øûäçኤŠó§§Ô^ÅÈí»È˜ùÐñ´±ÔMàŠüôØ£¡ÅédàÊçáÝàäÄö£øûýÂøÄëèüò—Ô^°äȘÔ@ñNúÕrÂØ£øÝ°øâmç§í«ý´ÅöÑ¥§Ô^ÅÈí»ÀÈüôDñÇÆ°°—ÚçáòúFFEƒª¤ãÎÅéä¡áèóçáƯÚÀÈ

ÀÀÀÀCTLE¤ëFFEÑ¥òúƒÅ僪¤ã¥¥ÅgȘѽDFEtòúñúƒÅ僪¤ã¥¥ÅgÀÈDFE¥¥Ågòúë´Ô^üÁÁbitçáéÅQŠó§ÎÛú¯bitçáéÅQÕøçÔMÅÅÅßí»È˜åOƤüâÚçáDFE¢èØåÆÅÅÏîaISIÎÅéäåš°èçáƯÚÀÈÕêùÝÐÆÖÆíȘöØ¥ìåOò¿Æûçá DFE ùÐñ´ò¿Æûè°ÕŸ^üççÀÈåÖýÕ¢Ç DFE çáçWáÈÅëøÛú¯È˜öØÆÅÝÄ؈üàêù§ãåùÐñ´çáá¢çáÀÈë´°ÈȘDFEÆùа—Ø£ÅÈí»øçȘࣤµÂóðäÚ¥Æç§ÔïéÅQÕøçøÅÈ´°˜Ô^åÕøççኤݣØÕÔï¡Ô£·Ôï1ȘçëÆÖåÕøççኤݣØÕÔïç룷Ôï0ÈˋÀÈØ·ÇùȘDFE ±¡áæÛú¯ÝàäÄçáéÅQÕøçÈ´å—ǵ£·§ççëÈˋ Șý¡ª±Ô@Åôçც¤ãÕøçŠó§Îý´ÅöøÄÅôäÅÅÔïéÅÁÀÈ üôûÌòúè°ÕŸ^ DFE ùÐñ´çáçWáÈÅëȤ

ÀÀÀÀV(k) = c1s(k ´C 1) + c2(k ´C 2)

ÀÀÀÀóðøÅȤ

ÀÀÀÀ• V(k) òúÅÈí»¤µçኤÕøçȘÆûÆÖéÅQÝàäÄö£øûKçáÔï ŸBòú1Ôòú0ÀÈ

ÀÀÀÀ• s(k-n) òúö£ÆÖÝàäÄö£øû k øÛú¯ n ÝàäÄäçáÔïøçÈ´Ôï ŸBÈˋÀÈ

ÀÀÀÀ• cn òúö£ÆÖ¡ÅédàÊÝàäÄö£øûøÛú¯ n ÝàäÄäçáÅÈí»üççÈ´°ÕŸ^üççÈˋÀÈ

ÀÀÀÀÎÆÖè°ÕŸ^ DFE ÚífȘÅÒ؈üàÇ_Ñ´Ûú¯ÝàäÄö£øûøÛú¯çáèÝàäÄçáÔï ŸBøçȘŠS¤µùÐñ´ÂÆûóðÝàäÄÔïøç°ùØåüÁˆçá°ÕŸ^üççȘ柤µâÜ¥ÆóÞÚȘçû°—Ûú¯ÝàäÄçáéÅQÕøçó¨Øóê¢È˜åSÑÁ DFE ùÐñ´Âåó¨Øóê¢øݧƈÆûç§Õø犤èüÀÈDFEí»Ç_¿Êæ¼çáú¯äÃòúüÁÁÝàäÄçáŠó§éÅQòúí»Ç_çáȘùªØåÎÆÖÅéäçáÅéåŠÝàÆÅأѴ؈úµÀÈ

ÀÀÀÀCTLE¤ëFFE çც¤ãó¼Åƒó˜(£·ùÐñ´)ý£üþò¿ÆûDFEçáŃó˜(£·ùÐñ´)áúÆëŠsȘÝàDFEŃó˜ÅÒ؈çáÕTŠôñ¡■èìȘطÇùåÖǵÑÁçúÕrüôȘåOÆàùTÑ¥±üàÔxþCTLE£·FFEçც¤ãñ§ñ´ÀÈѽåÖ¡■ëŠs¤ë¡ÔùìçáúÕrüôȘأ¯ÐúÕrüôòúüàÆûCTLE£·FFEÚ¯îÅéäîÜDÇ·Õ_ȘࣤµåìÆûDFEÔMØ£ý§£₤ÀÈ

ÀÀÀÀåÖñú°È¡Ôùì¤ëÕLƒÁŠxçáÅéä¼ïøÅȘ봰Èòú¯îŸA¥ÆøĤ냪¤ã¥¥Åg§Y¤üò¿ÆûÀÈòæüàåÖ¯lùëÑùäÃ軡ԟlñøê¢È˜§Ô^ë´çâçáp¤áç§Ô_§ÆòíÑù¤µÈ˜åìë´Ô^ƒª¤ã¥¥Åg¡áèóÅéäȘáѽ˜FÕLƒÁŠxÈ´>50cmÈˋÀ¡ÔùìÈ´ >10GbpsÈˋçáÅéä¼ïÀÈ

0

0

ÀÀ2019-07-25

ÀÀ2019-07-25

ÀÀ2019-07-25

ÀÀ2019-07-25

ÀÀ2019-07-12

ÀÀ2019-07-12

ÀÀ2019-07-12

ÀÀ2019-07-12

ÀÀ2019-07-12

ÀÀ2019-07-12

ÀÀ2019-07-11

ÀÀ2019-07-11

ÀÀ2019-07-10

ÀÀ2019-07-10

ÀÀ2019-07-10

ÀÀ2019-07-10

ÀÀ2019-07-09

ÀÀ2019-07-09

ÀÀ2019-07-08

ÀÀ2019-07-08

ÀÀ2019-07-05

ÀÀ2019-07-05

ÀÀ2019-07-04

ÀÀ2019-07-04

ÀÀ2019-07-03

ÀÀ2019-07-03

ÀÀ2019-06-26

ÀÀ2019-06-26

ÀÀ2019-06-26

ÀÀ2019-06-26

ÀÀ2019-06-26

ÀÀ2019-06-26

ÀÀ2019-06-21

ÀÀ2019-06-21

ÀÀ2019-06-18

ÀÀ2019-06-18

ÀÀ2019-06-18

ÀÀ2019-06-18

ÀÀ2019-06-18

ÀÀ2019-06-18